目录

- 1.行为描述

- 2.过程(procedural)块

- 3.过程赋值(procedural assignment)

- 4.过程时序控制

- 5.简单延时

- 6.边沿敏感时序

- 7.wait语句

微信公众号获取更多FPGA相关源码:

1.行为描述

- 行为级描述是对系统的高抽象级描述。在这个级别,表达的是输入和输出之间转换的行为,不包含任何结构信息。

- Verilog有高级编程语言结构用于行为描述,包括:wait, while, if then, case和forever。

- Verilog的行为建模是用一系列以高级编程语言编写的并行的、动态的过程块来描述系统的工作。

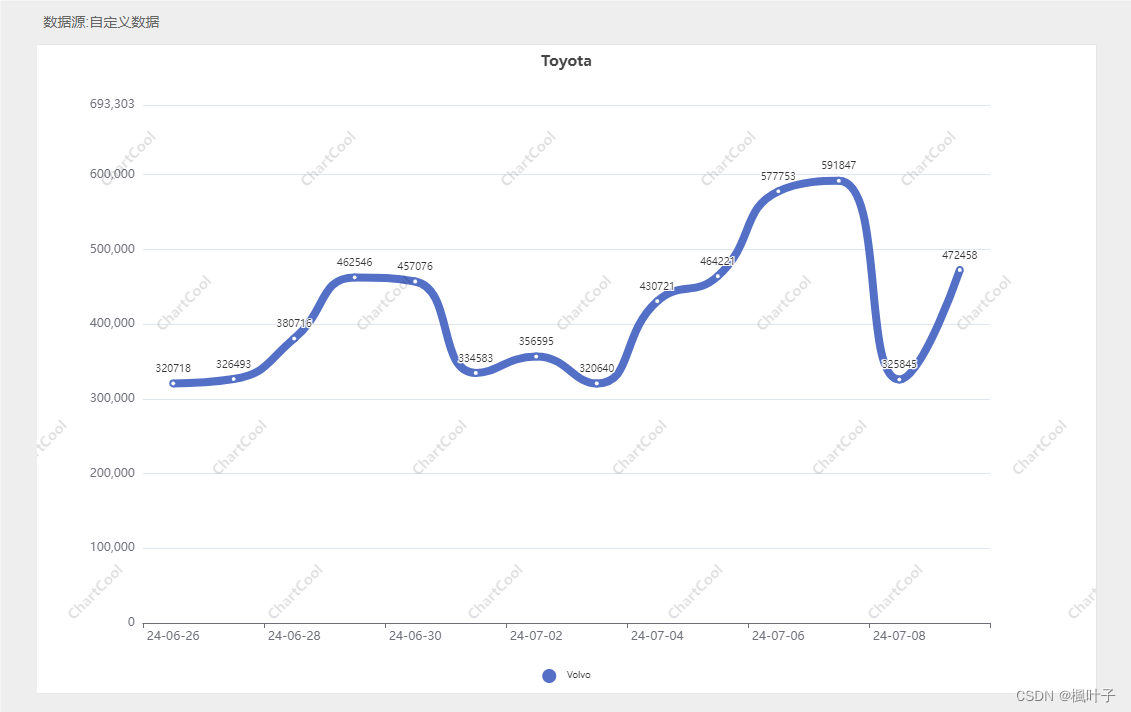

- 在每一个时钟上升沿,若Clr不是低电平,置Q为D值,置Qb为D值的反。

- 无论何时Clr变低,置Q为0,置Qb为1

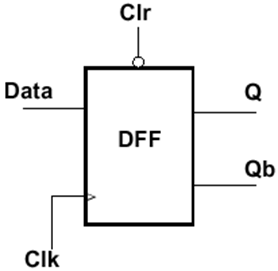

2.过程(procedural)块

- 过程块是行为模型的基础。

- 过程块有两种:

- initial块,只能执行一次

- always块,循环执行

- 过程块中有下列部件

- 过程赋值语句:描述过程块中的数据流

- 高级结构(循环,条件语句):描述块的功能

- 时序控制:控制块的执行及块中的语句。

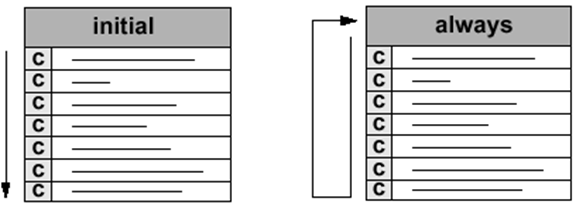

3.过程赋值(procedural assignment)

- 在过程块中的赋值称为过程赋值。

- 在过程赋值语句中表达式左边的信号必须是寄存器类型(如reg类型)

- 在过程赋值语句等式右边可以是任何有效的表达式,数据类型也没有限制。

- 如果一个信号没有声明则缺省为wire类型。使用过程赋值语句给wire赋值会产生错误。

module adder (out, a, b, cin);

input a, b, cin;

output [1:0] out;

wire a, b, cin;

reg half_sum;

reg [1: 0] out;

always @( a or b or cin)

begin

half_sum = a ^ b ^ cin ; // OK

half_carry = a & b | a & !b & cin | !a & b & cin ; // ERROR!

out = {half_carry, half_ sum} ;

end

endmodule

4.过程时序控制

在过程块中可以说明过程时序。过程时序控制有三类:

- 简单延时(#delay):延迟指定时间步后执行

- 边沿敏感的时序控制:@(<signal>)

- 在信号发生翻转后执行。

- 可以说明信号有效沿是上升沿(posedge)还是下降沿(negedge)。

- 可以用关键字or指定多个参数。

- 电平敏感的时序控制:wait(<expr>)

- 直至expr值为真时(非零)才执行。

- 若expr已经为真则立即执行。

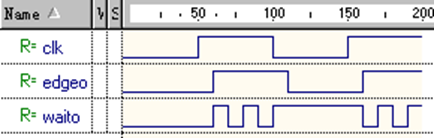

module wait_test;

reg clk, waito, edgeo;

initial begin

initial begin clk = 0;edgeo=0;waito=0;end

always #10 clk = ~clk;

always @(clk) #2 edgeo = ~edgeo;

always wait(clk) #2 waito = ~waito;

endmodule

5.简单延时

在test bench中使用简单延时(#延时)施加激励,或在行为模型中模拟实际延时。

module muxtwo (out, a, b, sl);

input a, b, sl;

output out;

reg out;

always @( sl or a or b)

if (! sl)

#10 out = a;

// 从a到out延时10个时间单位

else

#12 out = b;

//从b到out延时12个时间单位

endmodule

在简单延时中可以使用模块参数parameter,例如产生时钟:

module clock_gen (clk);

output clk;

reg clk;

parameter cycle = 20;

initial clk = 0;

always

#(cycle/2) clk = ~clk;

endmodule

6.边沿敏感时序

时序控制@可以用在RTL级或行为级组合逻辑或时序逻辑描述中。可以用关键字posedge和negedge限定信号敏感边沿。敏感表中可以有多个信号,用关键字or连接。

module reg_ adder (out, a, b, clk);

input clk;

input [2: 0] a, b;

output [3: 0] out;

reg [3: 0] out;

reg [3: 0] sum;

always @( a or b) // 若a或b发生任何变化,执行

#5 sum = a + b;

always @( negedge clk) // 在clk下降沿执行

out = sum;

endmodule

特别注意:事件控制符or和位或操作符 | 及逻辑或操作符 || 没有任何关系。

7.wait语句

wait用于行为级代码中电平敏感的时序控制。

下面 的输出锁存的加法器的行为描述中,使用了用关键字or的边沿敏感时序以及用wait语句描述的电平敏感时序。

module latch_adder (out, a, b, enable);

input enable;

input [2: 0] a, b;

output [3: 0] out;

reg [3: 0] out;

always @( a or b)

begin

wait (!enable) // 当enable为低电平时执行加法

out = a + b;

end

endmodule

特别注意:综合工具还不支持wait语句。

微信公众号获取更多FPGA相关源码: